# RF Noise in 0.18- $\mu$ m and 0.13- $\mu$ m MOSFETs

C. H. Huang, C. H. Lai, J. C. Hsieh, J. Liu, and Albert Chin, *Senior Member, IEEE*

**Abstract**—We have studied the gate finger number and gate length dependence on minimum noise figure ( $NF_{min}$ ) in deep sub-micrometer MOSFETs. A lowest  $NF_{min}$  of 0.93 dB is measured in 0.18- $\mu$ m MOSFET at 5.8 GHz as increasing finger number to 50 fingers, but increases abnormally when above 50. The scaling gate length to 0.13  $\mu$ m shows larger  $NF_{min}$  than the 0.18- $\mu$ m case at the same finger number. From the analysis of a well-calibrated device model, the abnormal finger number dependence is due to the combined effect of reducing gate resistance and increasing substrate loss as increasing finger number. The scaling to 0.13- $\mu$ m MOSFET gives higher  $NF_{min}$  due to the higher gate resistance and a modified T-gate structure proposed to optimize the  $NF_{min}$  for further scaling down of the MOSFET.

**Index Terms**—MOSFET, noise, RF, scaling trend, 0.13  $\mu$ m.

## I. INTRODUCTION

AS CONTINUOUSLY scaling down the VLSI technology, the RF gain of deep sub-micrometer MOSFET is improved so that it can be used for wireless communication. However, it is still not clear what the dependence of the scaling trend is on RF noise that limits the noise floor of an RF system. It is known that the noise figure ( $NF$ ) of current Si RF ICs is still larger than the GaAs counterpart, but the excess noise in Si ICs may come from the passive devices [1] that can be largely suppressed by using ion implantation processes developed by us [1]–[4]. Therefore, further reduction of noise in Si RF ICs close to GaAs depends on optimizing the active MOSFETs. In this paper, we have used multifingered layout and device scaling to optimize the RF noise in deep sub- $\mu$ m MOSFETs. A lowest minimum  $NF$  ( $NF_{min}$ ) of 0.93 dB is reached in 0.18- $\mu$ m MOSFET as increasing finger number to 50, but shows abnormal increase as finger number  $>50$ . The scaling to 0.13- $\mu$ m MOSFETs gives larger  $NF_{min}$  than 0.18- $\mu$ m devices at the same gate finger number. The abnormal finger dependence analyzed by a self-consistent dc,  $NF$ , and  $S$ -parameter model is due to the tradeoff between decreasing gate resistance ( $R_g$ ) and increasing substrate loss [1]–[4] as increasing finger number. The gate length dependence is due to the increasing  $R_g$  as scaling down from 0.18 to 0.13  $\mu$ m. However, the larger finger number will consume more device area and power that are opposite to the VLSI scaling trend. Besides, the current-gain cut-off frequency ( $f_T$ ) may also be degraded due to the increasing parasitic gate–body capacitance ( $C_{gb}$ ) used for contact. Thus, further scaling down of the

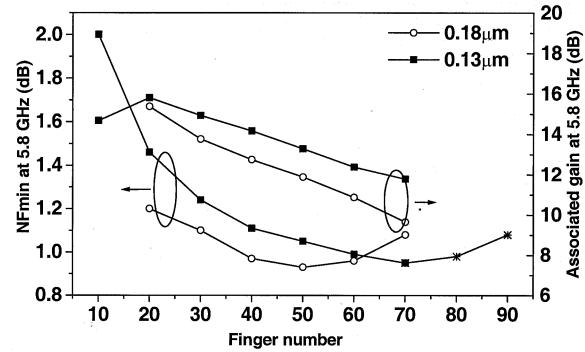

Fig. 1.  $NF_{min}$  and associated gain at 5.8 GHz of 0.18- and 0.13- $\mu$ m MOSFETs. The  $NF_{min}$  for gate finger number  $>70$  are obtained from simulation using the well-calibrated device model.

MOSFETs will generate larger noise unless a modified T-gate MOSFET structure is used.

## II. EXPERIMENTAL PROCEDURE

To optimize the  $NF_{min}$  of MOSFETs, we have used multi-fingered layout and scaled gate length from 0.18 to 0.13  $\mu$ m, where the finger number is from 10 to 70 with 5- $\mu$ m finger width. This 5- $\mu$ m finger width is chosen by trading off reducing  $R_g$  and increasing parasitic  $C_{gb}$  used for silicide gate–metal contact. Because the  $f_T$  equals  $g_m/2\pi(C_{gs} + C_{gb})$ , the use of too short a finger width with too many finger numbers will increase the  $C_{gb}$  and reduce the  $f_T$ . The fabricated MOSFETs are first characterized by dc  $I$ – $V$  measurements. Then, standard  $S$ -parameters are measured up to 20 GHz using a HP8510B network analyzer and on-wafer probes, de-embedded from the probe pad. The  $NF_{min}$  and associate gain are measured using ATN-NP5B Noise Parameter Extraction System up to 7.2 GHz that covers the most important frequency range for wireless communication.

## III. RESULTS AND DISCUSSIONS

Fig. 1 shows the finger and gate length dependence on measured  $NF_{min}$  and the associate gain at 5.8 GHz for 0.13- and 0.18- $\mu$ m MOSFETs. It is noticed that when scaling down the MOSFET from 0.18 m to 0.13  $\mu$ m, the associate gain increases but also gives higher  $NF_{min}$  that is highly undesired. A lowest  $NF_{min}$  of 0.93 dB is obtained in 0.18- $\mu$ m MOSFETs with 50 fingers, which is close to or better than the data published in the literature [5]–[10] and compatible with GaAs HEMTs [11]. The  $NF_{min}$  in 0.13- $\mu$ m MOSFETs decreases monotonically while increasing gate fingers to 70, and a similar trend of decreasing  $NF_{min}$  while increasing fingers is also found in 0.18- $\mu$ m MOSFETs, but shows an abnormal increase as finger number  $>50$ .

To understand such abnormal dependence on gate finger and length, we have used a self-consistent dc,  $NF$ , and  $S$ -param-

Manuscript received March 1, 2002; revised July 10, 2002. This work was supported by the UMC and by the NSC under 90-2215-E-009-052. The review of this letter was arranged by Associate Editor Dr. Arvind Sharma.

C. H. Huang, C. H. Lai, and A. Chin are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan.

J. C. Hsieh and J. Liu are with United Microelectronics Cooperation, Hsinchu, Taiwan.

Digital Object Identifier 10.1109/LMWC.2002.805930

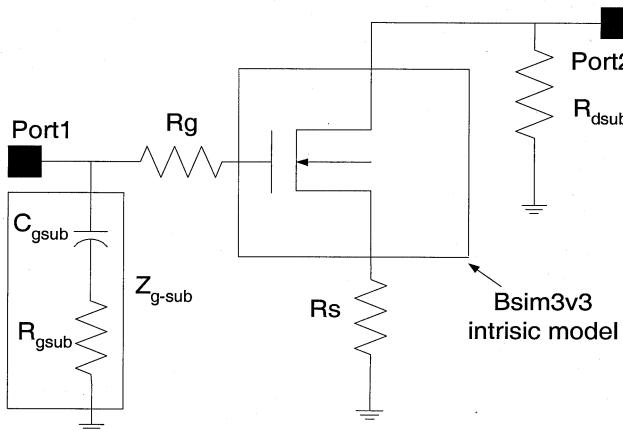

Fig. 2. Equivalent circuit model for 0.18- and 0.13- $\mu$ m MOSFETs.

eter equivalent circuit model shown in Fig. 2 to simulate the devices and extract the important parameters. The device model contains an intrinsic BSIM3v3 model, additional  $R_g$  to gate, and additional shunt impedances to simulate the substrate loss. The suitability of this equivalent circuit model is examined from the good agreement between measured and modeled data shown below.

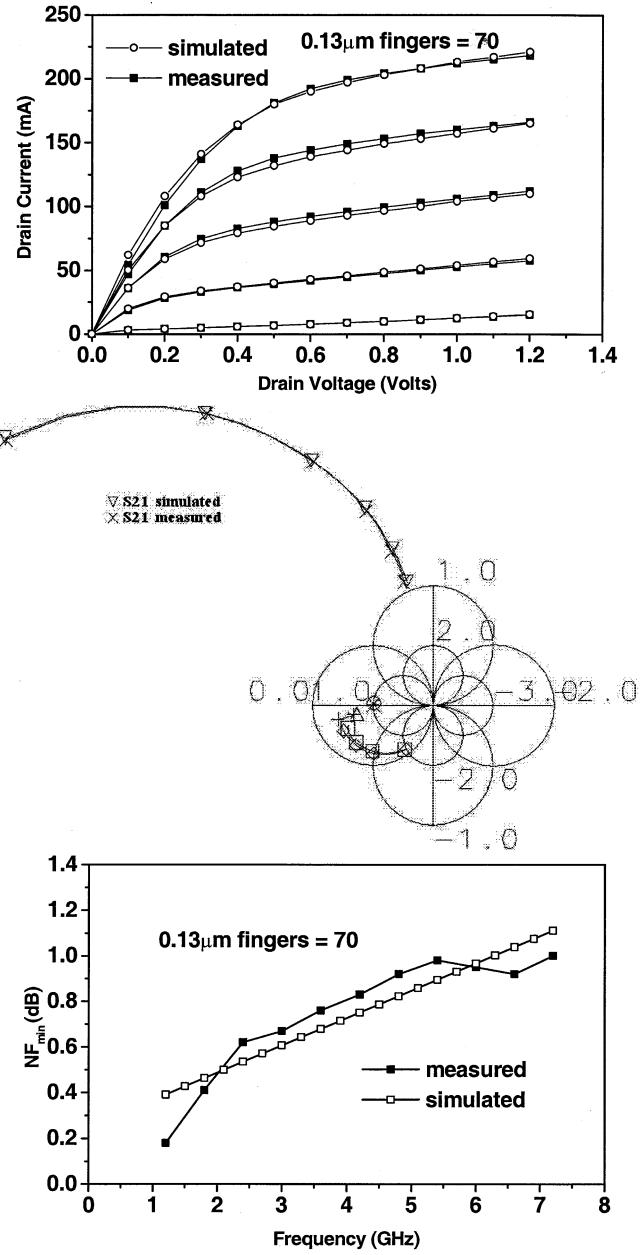

Fig. 3(a)–(c) shows the measured and simulated  $I_D$ – $V_D$  characteristics,  $S$ -parameters up to 20 GHz, and  $NF_{\min}$  up to 7.2 GHz of 0.13- $\mu$ m MOSFETs with the largest finger number of 70. Good agreements between simulated and measured dc  $I_D$ – $V_D$ ,  $S$ -parameters, and  $NF_{\min}$  are obtained for 0.13  $\mu$ m MOSFETs with 70 fingers. Similar good agreements between measured and modeled dc  $I_D$ – $V_D$ ,  $S$ -parameters, and  $NF_{\min}$  are also obtained in other finger numbers of 0.13- $\mu$ m MOSFETs and all finger numbers of 0.18- $\mu$ m MOSFETs (not shown). The good agreement between measured and modeled data for various gate finger numbers and gate length indicate the excellent accuracy of the equivalent circuit model that can be further used for device parameter extraction [3], [10].

Because the RF signal is input from the gate and amplified after passing through the output drain terminal, the dominant noise source is from the gate input terminal. This is because the noise in an amplification system is due to following equation [12]:

$$NF_T = NF_1 + \frac{NF_2 - 1}{G_1} + \dots + \frac{NF_N - 1}{G_1 G_2 \dots G_{N-1}}.$$

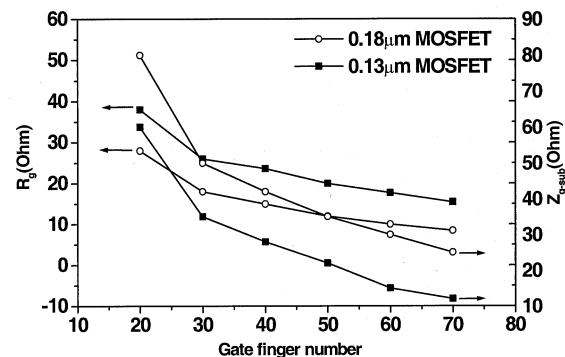

Thus, the noise of the system with amplification is governed by the input stage, where  $G_i$  is the gain of each stage amplifier. Fig. 4 shows the dependence of extracted  $R_g$  and gate substrate loss impedance ( $Z_{g-sub}$ ) on gate fingers. A decreasing gate resistance as increasing finger number is observed is due to the parallel effect and explains the decreasing  $NF_{\min}$  as the increasing finger number. From our device simulation, the reason for abnormally increasing  $NF_{\min}$  when gate finger  $> 50$  in 0.18- $\mu$ m MOSFETs is due to the decreasing  $Z_{g-sub}$  because of the large area-related substrate loss. The higher  $R_g$  in 0.13- $\mu$ m MOSFETs also explains the higher  $NF_{\min}$  while decreasing the gate length from 0.18 to 0.13  $\mu$ m because of

Fig. 3. The simulated and measured (a) dc  $I_D$ – $V_D$  characteristics, (b)  $S$ -parameters, and (c)  $NF_{\min}$  of 0.13- $\mu$ m MOSFETs with the largest 70 fingers.

Fig. 4. Dependence of the gate finger number on the gate resistance  $R_g$  and substrate loss impedance  $Z_{g-sub}$  of 0.18- and 0.13- $\mu$ m MOSFETs.

the smaller gate area. From the extrapolated data of  $0.13\text{-}\mu\text{m}$  MOSFETs and the well-calibrated device model, similar increasing noise figure after increasing gate finger  $>70$  is also obtained, as shown in Fig. 1. This sets the upper limit of the increasing gate finger even without considering the device area and power consumption. Therefore, further scaling down the gate length will give a higher  $NF_{\min}$  even though the associate gain is increased, unless a modified T-gate MOSFET structure is used.

#### IV. CONCLUSION

We have found a strong dependence of  $NF_{\min}$  on a layout finger number and gate length that is due to the combined effect of  $R_g$  and substrate loss effect. A T-gate structure is necessary to reduce the RF noise for further scaling down the MOSFETs.

#### REFERENCES

- [1] K. T. Chan, A. Chin, C. M. Kwei, D. T. Shien, and W. J. Lin, "Transmission line noise from standard and proton-implanted Si," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 2000, pp. 763–766.

- [2] Y. H. Wu, A. Chin, K. H. Shih, C. C. Wu, S. C. Pai, C. C. Chi, and C. P. Liao, "RF loss and cross talk on extremely high resistivity (10K–1M-cm) Si fabricated by ion implantation," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 2000, pp. 241–244.

- [3] K. T. Chan, A. Chin, Y. B. Chen, Y.-D. Lin, D. T. S. Duh, and W. J. Lin, "Integrated antennas on Si, proton-implanted Si and Si-on-quartz," in *IEDM Tech. Dig.*, 2001, pp. 903–906.

- [4] Y. H. Wu, A. Chin, K. H. Shih, C. C. Wu, C. P. Liao, S. C. Pai, and C. C. Chi, "The fabrication of very high resistivity Si with low loss and cross talk," *IEEE Electron Device Lett.*, vol. 21, pp. 394–396, 2000.

- [5] J. N. Burghartz, M. Hargrove, C. S. Webster, R. A. Groves, M. Keene, K. A. Jenkins, R. Logan, and E. Nowak, "RF potential of a  $0.18\text{-}\mu\text{m}$  CMOS logic device technology," *IEEE Trans. Electron Devices*, vol. 47, pp. 864–870, Apr. 2000.

- [6] H. Iwai, "CMOS technology for RF application," in *Proc. IEEE Int. Conf. Microelectron.*, 2000, pp. 27–34.

- [7] C. C. Enz and Y. Cheng, "MOS transistor modeling for RF IC design," *IEEE Trans. Solid-State Circuits*, vol. 35, pp. 186–201, Feb. 2000.

- [8] N. Zamdmer, A. Ray, J.-O. Plouchart, L. Wagner, N. Fong, K. A. Jenkins, W. Jin, P. Smeys, I. Yang, G. Shahidi, and F. Assaderaghi, "A  $0.13\text{-}\mu\text{m}$  SOI CMOS technology for low-power digital and RF applications," in *Proc. VLSI Symp. Tech.*, 2001, pp. 85–86.

- [9] J. J. Ou, X. Jin, C. Hu, and P. R. Gray, "Submicron CMOS thermal noise modeling from an RF perspective," in *Proc. VLSI. Symp. Tech.*, 1999, pp. 151–152.

- [10] Y. H. Wu, A. Chin, C. S. Liang, and C. C. Wu, "The performance limiting factors as RF MOSFET's scaling down," in *Int. RF-IC Symp.*, 2000, pp. 151–155.

- [11] R. Follmann, J. Berben, D. Köther, P. Waldow, J. Borkes, and I. Wolff, "A universal method for calculating and extracting the LF and RF noise behavior of nonlinear devices," in *IEEE GaAs Dig.*, 2000, pp. 47–51.

- [12] R. Pettai, *Noise in Receiving Systems*. New York: Wiley, 1984, p. 132.